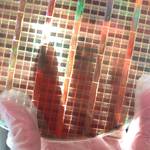

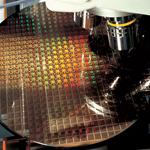

三維晶片(3D IC)可望擴大普及。半導體設備商Veeco日前發布新一代濕式蝕刻設備,將化學機械研磨(CMP)、電漿蝕刻、矽厚度量測與清洗等四種製程工序合而為一,可較傳統乾式蝕刻的方法,顯著減少3D IC關鍵製程技術–矽穿孔(TSV)的成本,同時降低缺陷發生情形,將有助提升半導體廠採納3D IC設計的意願。

|

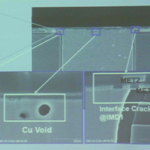

| Veeco精密表面處理技術長Laura Rothman Mauer表示,濕式蝕刻亦可消除過去晶圓研磨後所造成的表面下損壞,同時也能確保穿孔與襯底氧化層的完整性。 |

Veeco精密表面處理(PSP)技術長Laura Rothman Mauer表示,美光(Micron)、SK海力士(SK Hynix)、三星(Samsung)和賽靈思(Xilinx)已利用TSV開發出3D IC,而今年8月,Novati和東芝(Toshiba)也以TSV打造出3D IC,可見晶片設計逐漸朝向3D IC發展。

雖然多家廠商已透過TSV成功開發3D IC,並改善諸多問題,但TSV仍面臨到高成本的課題,有鑑於此,Veeco改變過去利用CMP與乾式蝕刻的方式,而採用濕式蝕刻製程來達成TSV。由於該公司的濕式蝕刻製程解決方案將CMP、電漿蝕刻、矽厚度量測與清洗工具等四製程合而為一,因而更進一步降低TSV成本。

Mauer援引SavanSys的分析資料指出,該公司的濕式蝕刻與傳統作法(基準乾式蝕刻)相比,毋須經過CMP的步驟,加上已於過程中進行量測,以及不用額外清洗,因此每一片晶圓總成本得以從68.5美元降至61.84美元。

據了解,濕式蝕刻製程分為兩階段,第一階段利用混合式藥劑進行旋塗蝕刻,達到表面光滑與消除磨痕,讓矽厚度輪廓得以均勻展現;第二個階段則利用新的顯影劑–SACHEM Reveal Etch來均勻顯露TSV,同時不會對襯底氧化層或含金屬通孔造成損壞;比起以往步驟,第二階段的技術讓蝕刻變得更安全與環保,並可提升蝕刻速率。

Mauer解釋,除了成本降低、安全與環保等優勢外,廠商也會因濕式蝕刻製程可讓晶圓表面更平滑和降低粗糙度等考量,而採用該製程。據悉,目前市場上已有半導體廠商對此製程感到興趣。

Mauer表示,該公司未來的濕式蝕刻製程研發藍圖,將朝在UMB/Bumping的步驟,發展晶種層(Seed Layer)蝕刻等方向努力,讓相關技術更為先進。

另外,伴隨著新的濕式蝕刻設備推出,Veeco也研發出新的濕式蝕刻藥劑,它比過去的顯影劑(TMAH)更為安全。Mauer透露,Veeco與SACHEM在多年前合作時,便顧慮到TMAH的安全性,加上美國開始禁止使用高濃度的TMAH,所以很早之前SACHEM便著手研發替代TMAH的藥劑。